Rev1 Assembly Notes

Debug board

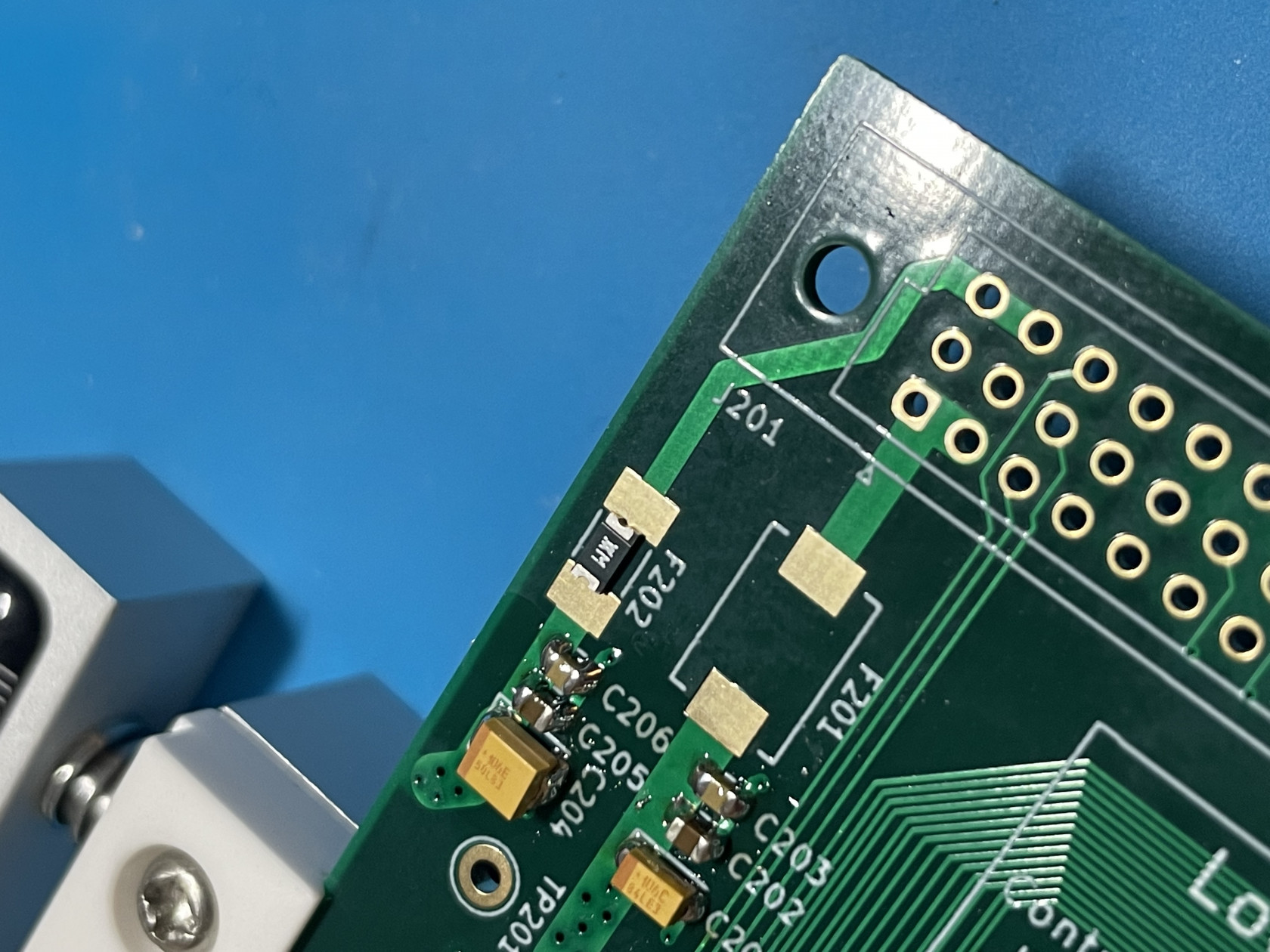

- F202 footprint appears to be too large for the fuse ordered (NANOSMDC050F/13.2-2)

- F201 is actually 1.1A, not 1.5A as the schematics indicate

- Caps under Teensy (C316/C317) could use with being moved a bit

- U508/U509 package sucks ass

- C512/C511 should be further away from IC in -Y

- The indications for RESET and HALT are inverted (D401, D402) from what they should be

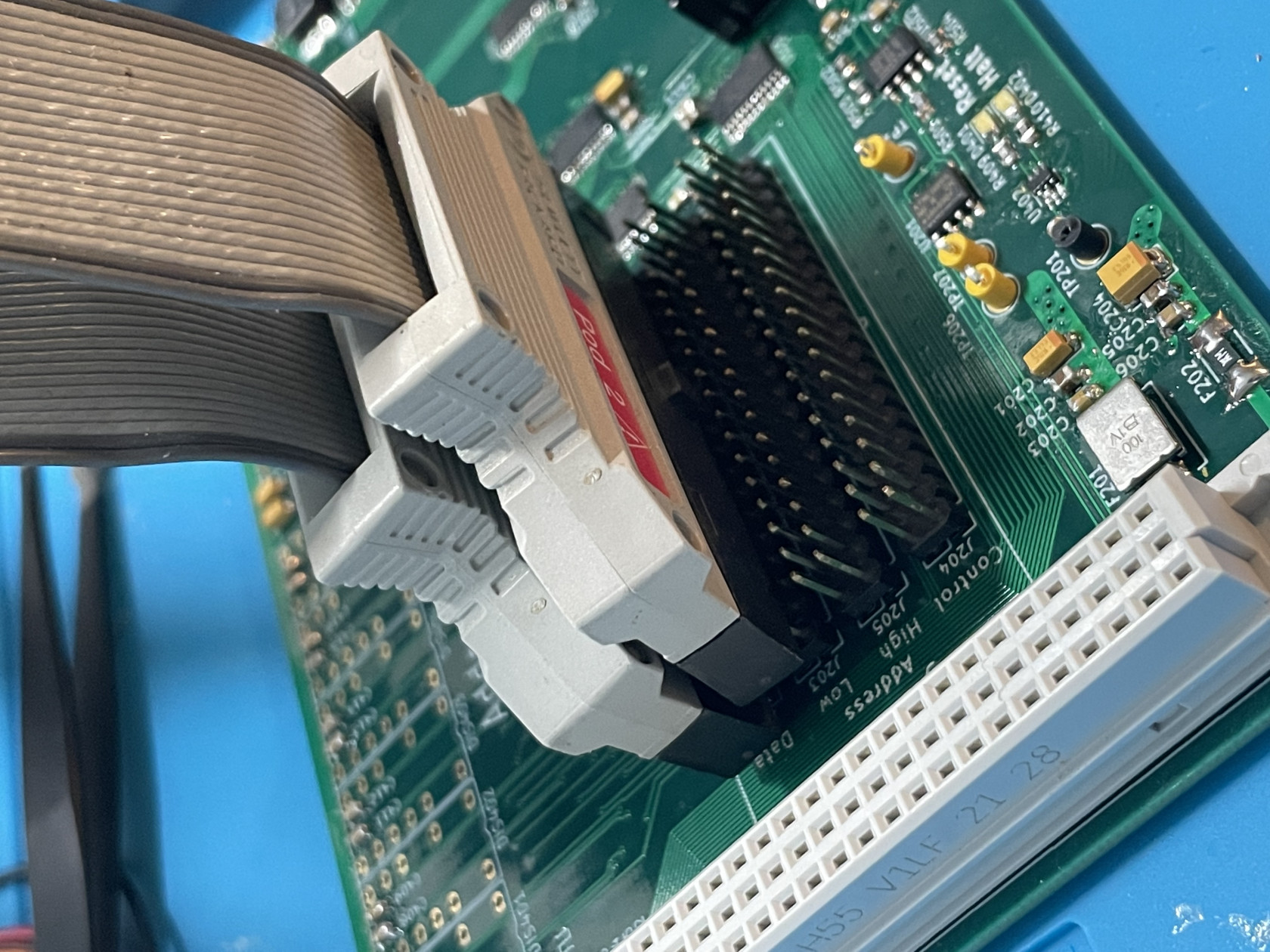

- Teensy USB port interferes with J302 with some USB cables

- Solder pads for DIN connectors could be slightly wider copper

- Logic probe connectors need more spacing in Y direction to fit the probes

No Comments